pub手册4.4.5.3.2,读取位去偏移(Read Bit De-skew)算法,该算法用于调整和校准 DDR 内存中数据位(DQ)之间的时序差异,确保所有的数据位在时序上对齐,以减少由于时序偏移(skew)造成的读写错误。

1. 概述

Read Bit De-skew 是为了 调整所有字节通道(byte lanes)中的数据位的时序偏差,使得各个数据位(例如 DQ 信号)在物理层上的传输时序得到对齐,防止由于时序误差导致读取数据出错。

2. 所需的条件

- 单个 Rank(内存通道)访问:这个算法仅对一个 Rank 进行操作,而不是多个 Rank。Rank 可以通过

DTCR.DTRANK寄存器来定义。 - 使用可编程地址进行内存访问:该算法使用了最多四个可编程寄存器(

DTAR0到DTAR3)来定义内存访问的起始地址。每个地址包含 bank、row、column 的信息,这些地址将用于进行内存的读取和写入操作。

3. DTAR 寄存器

DTAR0-3:这些寄存器定义了四个内存起始地址,用于执行数据位去偏移算法。- Bank和行(Row)地址:所有的

DTARn寄存器必须使用相同的 bank和行地址。 - 列地址(Column Address):在每个地址中,列地址的低三位([2:0])推荐设置为

3'b000,这样可以确保对 8 个连续的内存地址进行访问。

- Bank和行(Row)地址:所有的

4. 写入操作(Write Operation)

- 顺序的写入操作:算法使用一系列固定连续的写操作,这有助于产生一个降低了同频串扰(SSO,Simultaneous Switching Output)的数据模式。SSO 是由于多个信号同时切换状态时引发的噪声,降低 SSO 可以提高时序的稳定性。

- 0 到 1 的过渡:对于奇数位和偶数位的写操作,分别在不同的内存地址之间进行 0 到 1 的过渡,以产生 0-1 过渡的模式。

- 写入操作包括 8 次 BL8(或者 16 次 BL4)写入。BL8 和 BL4 指的是 突发长度(Burst Length),分别表示每次写入 8 个或 4 个连续的数据单元。

5. 读取操作(Read Operation)

- 顺序的读取操作:读取操作与写入操作类似,也是按顺序执行的,且同样用于生成降低了 SSO 的数据模式。

- 0 到 1 的过渡:类似写入操作,读取操作也会通过在不同的内存地址之间对奇数位和偶数位进行 0 到 1 的过渡,以保证数据位时序的一致性。

- 读取操作包括 4 次 BL8(或者 8 次 BL4)读取,每次读取都会返回 32 个数据单元(通常称为“数据节拍(beat)”),这些数据将返回给 PHY(物理层)进行进一步处理。

6. 读取时序的比较(Comparison of Data Beats)

在执行读取操作时,返回的 32 个数据节拍(beat)中,只有 特定范围的数据 会被用来进行比较和对齐:

- 假设数据节拍的编号为 0 到 31,那么只有 节拍 4 到 11 和 20 到 27 会被比较。

- 这意味着,读取的 32 个数据节拍中,只有一部分会被用来检查数据位的时序,帮助进行去偏移调整。

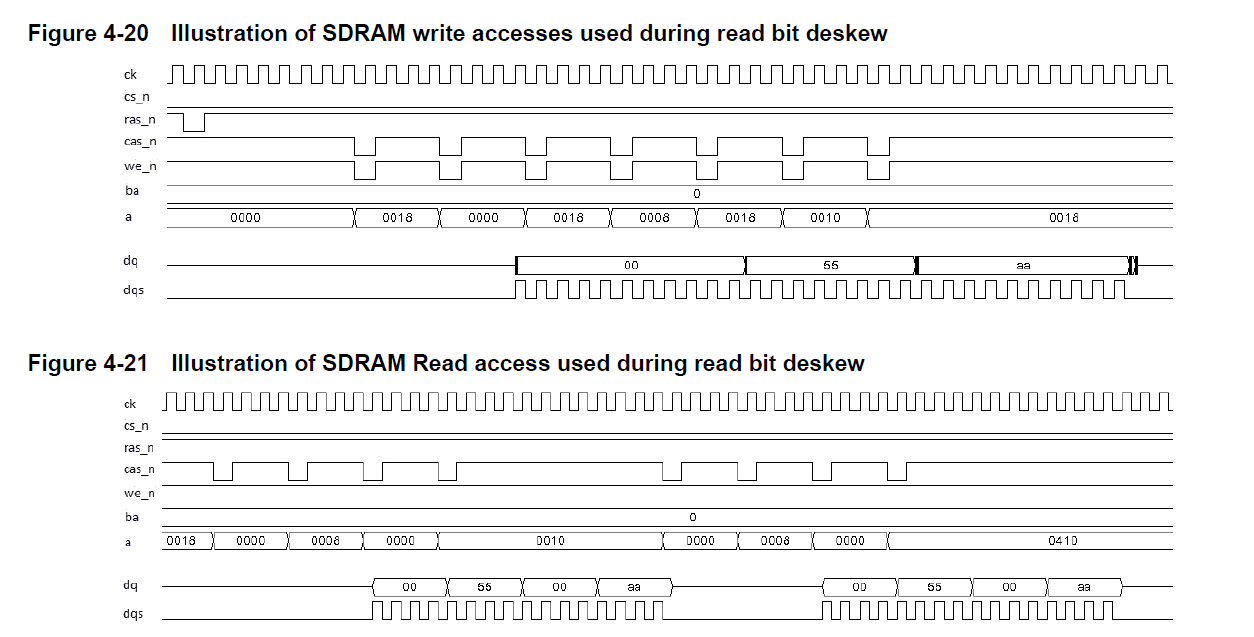

7. 写入和读取的示意图

Read Bit De-skew 算法的目标是对齐每个数据位(DQ)在读取路径中的 0 到 1 的过渡,也就是消除数据位在时序上的偏差(skew),确保数据的正确读取。

主要步骤和目标:

1.目标:

- 该算法的目标是 对齐数据位的 0 到 1 过渡,即保证每个数据位的读取时序正确,不偏离目标时序。

- 主要通过检测 数据眼(Data Eye)的边缘位置,确保所有数据位的读取时序对齐。

2.写入序列(Write Sequence):

- 在开始读取位去偏移之前,算法首先执行一个 写入序列,将数据写入内存的三个预定地址:

DTAR0(x0000)、DTAR1(x0008)和DTAR2(x0010)。 - 写入序列的作用是 确保数据正确写入,并为后续的读取操作提供正确的参考数据。

- 需要注意的是,这个写入序列 可选 地在写时序调整(Write Leveling Adjustment)之前执行。如果需要,可以通过

DTCR.DTEXD寄存器 增加额外的一个时钟周期(Cycle),以延长写时钟 DQS。

3.读取位去偏移算法(Read Bit De-skew):

写入完成后,接下来的操作都为 读取操作,这些读取操作用于执行去偏移(De-skew)调整。

检测数据眼的左边缘:算法首先需要检测数据眼的左边缘。左边缘指的是 DQS/DQS# 的时序位置,算法检测到至少有一个数据位出现读取失败时,就定位到这个位置。

- 读取失败意味着数据位与时钟的对齐出现了偏差,导致无法正确读取数据。

右移数据位:在检测到左边缘后,算法将每个位右移,直到在读取过程中检测到失败(即数据读取不成功)。检测失败的次数由寄存器

DTCR.DTRPT中的值定义,表示读取失败的次数阈值。- 这一步是通过不断调整数据位的位置,找出在每个数据位上造成失败的时序点,从而进行校准。

4.定位数据眼右边缘:

- 在每个数据位去偏移后,算法还会进一步“扫描”读取数据眼(read data eye),定位 数据眼的右边缘,即数据读取过程中成功接收数据的最右边界。

- 一旦检测到右边缘的位置,算法就会计算出 数据眼的中心。数据眼的中心是指 DQS/DQS# 信号应该对齐的位置。

5.确定 DQS 的位置:

- 当数据眼的中心位置计算完成后,DQS 信号会被放置在数据眼的中心位置,确保所有的数据位在读取时能正确对齐到 DQS。

关键寄存器和概念:

- **

DTCR.DTRPT**:该寄存器定义了读取位去偏移算法中,必须进行多少次读取失败检测才能结束偏移校准。也就是说,如果一个数据位的读取在连续n次尝试中都失败,则认为该数据位的时序存在问题。 - **

DTCR.DTEXD**:该寄存器控制是否在写时序调整之前延长 DQS 信号的一个周期,用于微调写时序。 - 数据眼(Data Eye):是指在读取过程中,数据位与时钟信号(DQS)之间的有效时序窗口。在这个窗口内,数据可以被正确地读取。如果数据位在窗口外,就会导致读取失败。

本文链接: https://talent-tudou.github.io/2024/11/25/DDR/Data Training-Read Bit De-skew/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!